第 16 章 存储器组织--内存

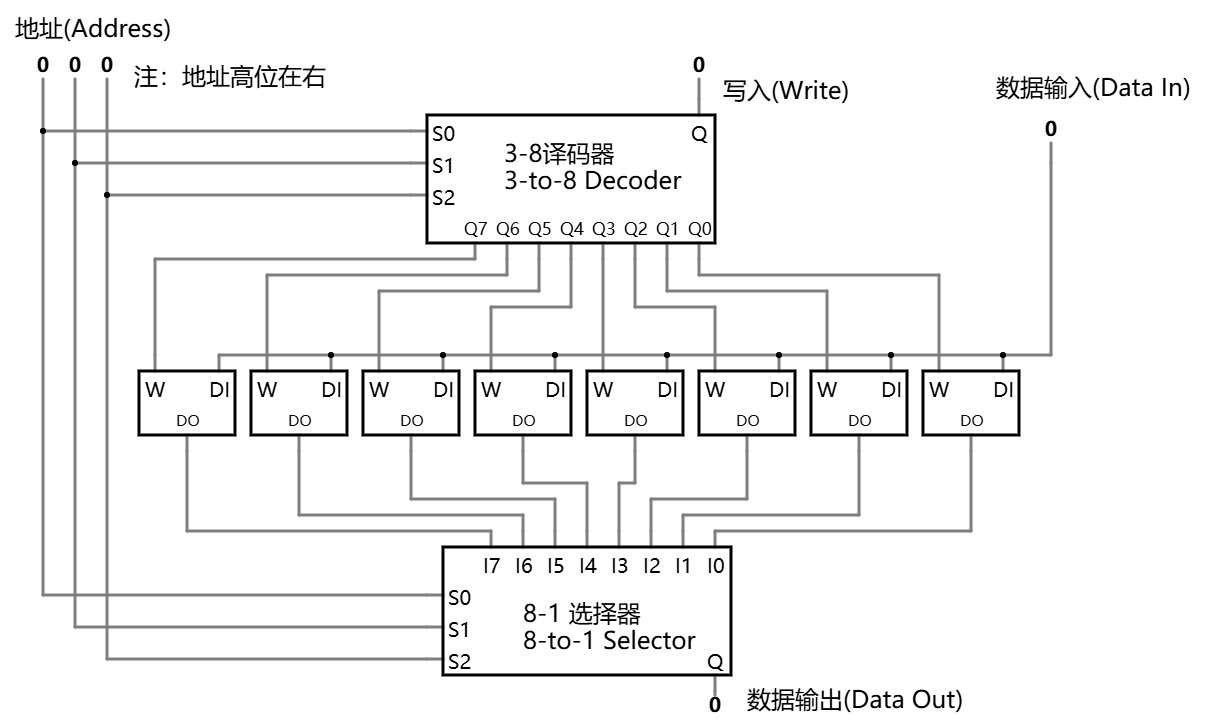

内存内部结构

操作说明

译码器用于写入, 操作同上

选择器用于输出, 操作同上

地址信号同时控制译码器和选择器, 注意地址的高位在右(比如 001 实际是 100, 选择的是 Q6 和 I6)

缺省情况下, 内部数据全是 0. 读者可先通过译码器写入, 再通过选择器输出

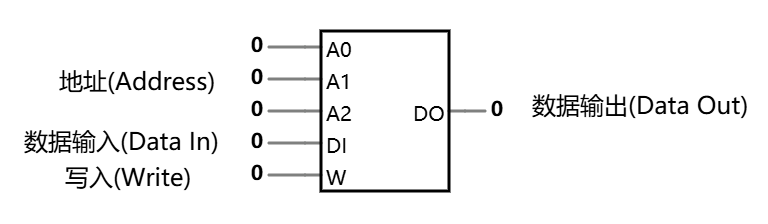

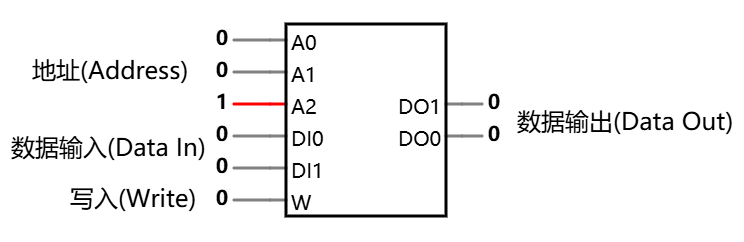

8x1 RAM

操作说明

操作同上, 是对上述电路的一个封装

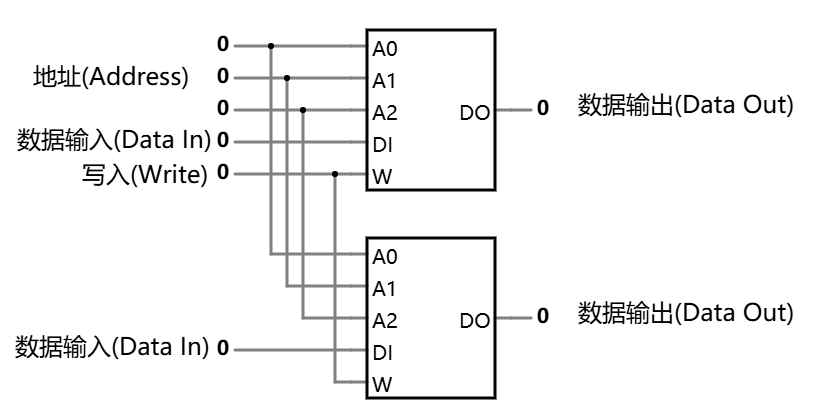

8x2 RAM 阵列

操作说明

地址信号和写入信号同时控制两个 8x1 RAM, 构成一组, 可一次性读入或输出两比特, 其余操作同上

8x2 RAM 阵列模型

操作说明

对上述电路的进一步封装, 操作同上

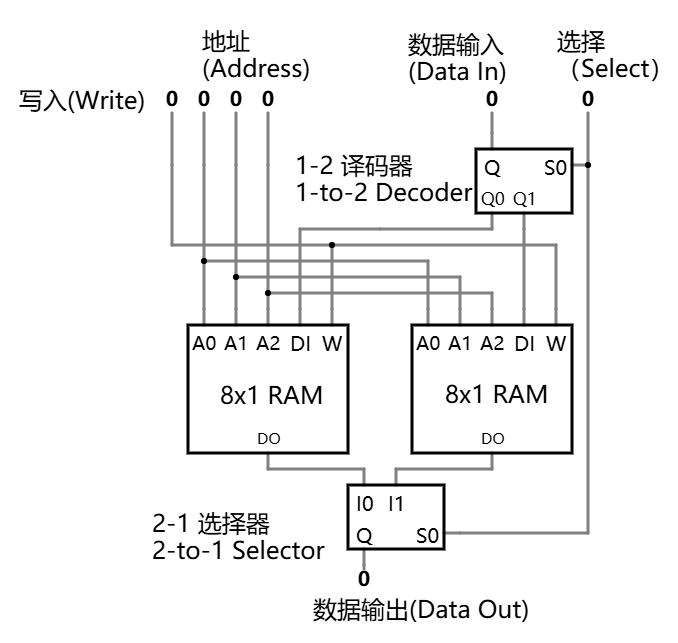

16x1 RAM 内部结构

操作说明

由两个 8×1 RAM 并排构成, 左边保存低 8 位, 右边保存高 8 位

由 "选择" 信号经译码器控制数据输入的存储位置, 0 时存左边, 1 时存右边

输出同样由 "选择" 信号经选择器控制, 0 时输出左边, 1 时输出右边

"选择" 信号相当于地址 A3, 因为有 16 个位置, 所以需要 4 根地址线

其余操作同上

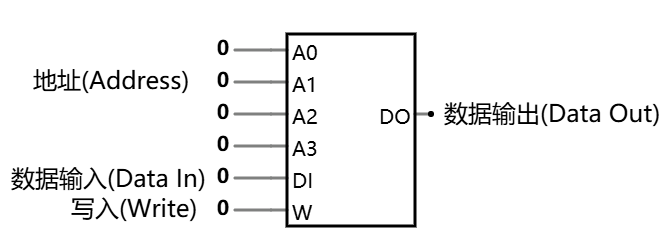

16x1 RAM 模型

操作说明

对上述电路的封装, 操作同上

此处 A3 相当于前述例子的 "选择" 信号

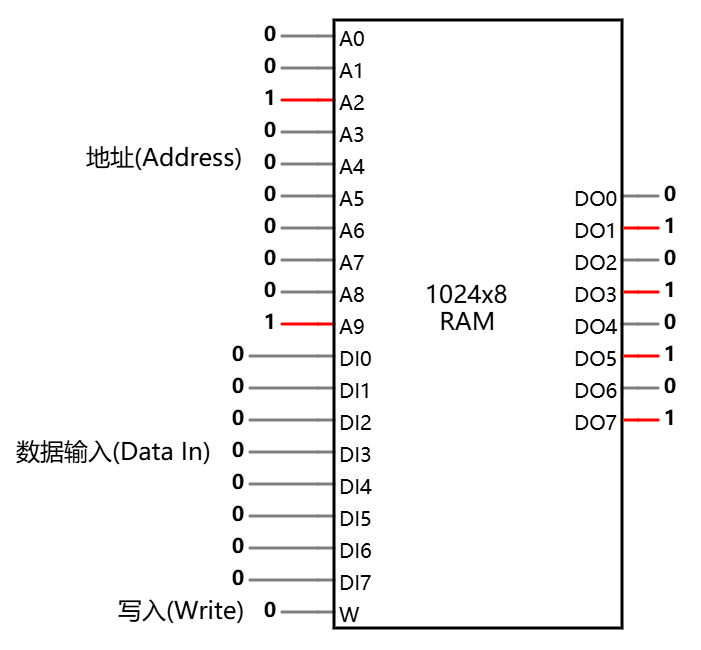

1024x8 RAM 模型

操作说明

将地址和输入输出同时按前述原则扩展后得到

可一次性读取 1 字节(8比特)数据, 并且有 1024 组空间(也即 1 KB)可读写

注: 此处内部直接使用了系统自带的内存模块实现, 而没有通过子电路封装的形式去实现, 因为数量太多了.