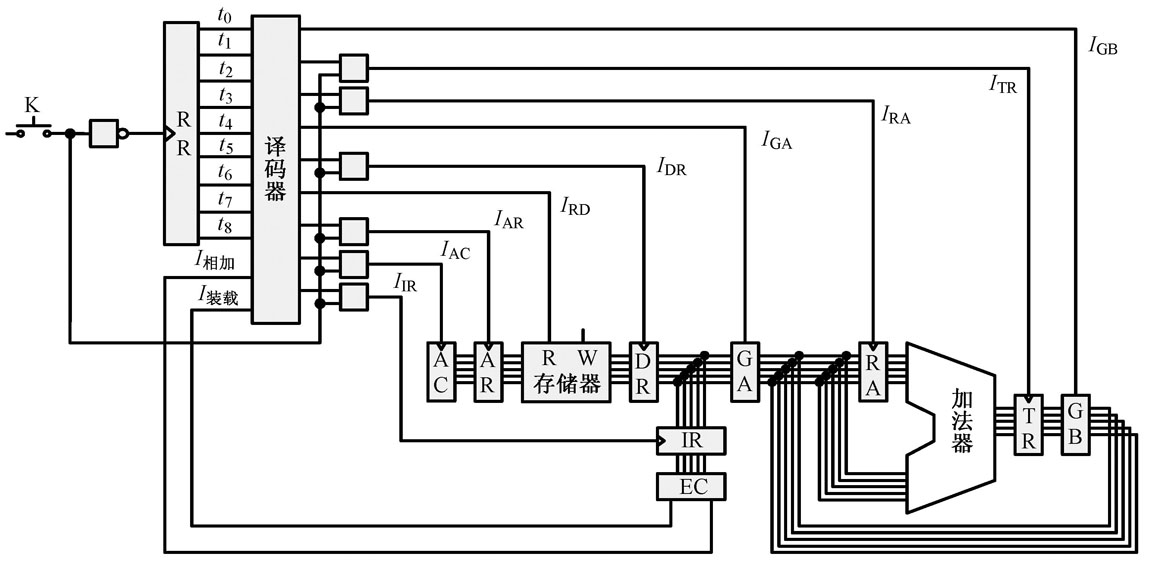

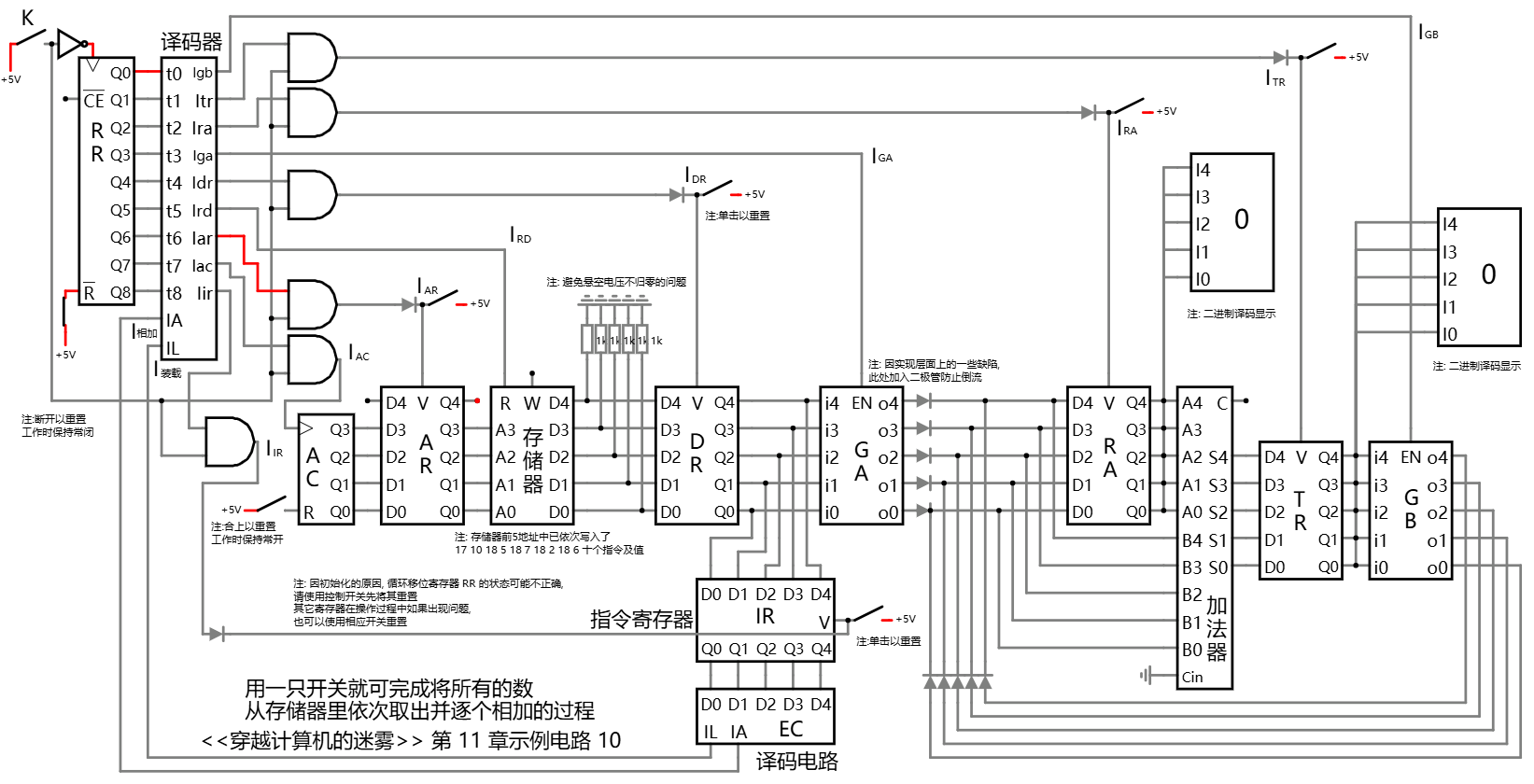

第11章 全自动加法计算机--一只开关取数并相加

用一只开关就可完成将所有的数从存储器里依次取出并逐个相加的过程.

操作说明

增加了 指令寄存器 和 译码电路, 扩充了 RR 循环移位寄存器

存储器中前 10 个地址已经提前写入了指令和数值, 其中 17(10001) 代表装载指令, 18(10010) 代表相加指令, 其它则为要加的数.

需检查地址计数器 AC 的值是否为零, RR 循环移位寄存器 Q0 是否为 1. 其它寄存器不为零的也需要先清零.

另: 增加了一些过程中的二进制转十进制译码输出, 方便观察整个运行过程

注: 读者如想仔细观察整个过程, 也可将按钮开关 K 调整为普通开关, 完全自主控制其按下和松开的过程.

初始状态 RR 寄存器 Q0=1, 译码器 Iar=1, 准备锁存第一个地址;

第一次按动开关 K, 寄存器 AR 存储第一个地址 0000, RR 寄存器 Q1=1, 译码器 Ird=1, 存储器第一个装载指令 10001 被读出, Ird=1 准备锁存该指令;

第二次按动开关 K, 寄存器 DR 将第一条装载指令保存, RR 寄存器 Q2=1, 译码器 Iac=1, 准备增加地址计数;

第三次按动开关 K, RR 寄存器 Q3=1, 译码器 Iir=1, 准备将指令锁存; 地址计数器 AC 加一, 变成 0001;

第四次按动开关 K, 指令寄存器 IR 将第一条装载指令保存, 并送入译码电路 EC, EC 译码并输出 IL=1, RR 寄存器 Q4=1, 译码器输入 IL=1, 输出 Iar=1, 准备锁存第二个地址;

第五次按动开关 K, 寄存器 AR 存储第二个地址 0001, RR 寄存器 Q5=1, 译码器输出 Idr=1, Ird=1, 存储器读出第二个地址中的操作数 10(也即第一个装载指令所要载入的数)

第六次按动开关 K, 寄存器 DR 存储操作数 10, RR 寄存器 Q6=1, 译码器输出 Iac=1;

第七次按动开关 K, 地址计数器 AC 再加一, RR 寄存器 Q7=1, 译码器输出 Ira=1, Iga=1, 传输门 GA 打开, 数据到达寄存器 RA 的输入端;

第八次按动开关 K, RR 寄存器 Q8=1, 寄存器 RA 把值存储并送入加法器 A 输入端.

第九次按动开关 K, RR 寄存器 Q0=1, 完成一次循环; 译码器 Iar=1;

第十次按动开关 K, RR 寄存器 Q1=1, 寄存器 AR 保存地址 0010, 译码器 Idr=Ird=1, 存储器读出第三个地址存储的相加指令;

第十一次按动开关 K, RR 寄存器 Q2=1, 寄存器 DR 保存相加指令并送到指令寄存器 IR 的输入端;

第十二次按动开关 K, RR 寄存器 Q3=1, 地址计数器 AC 再加一, 译码器 Iir=1;

第十三次按动开关 K, 指令寄存器 IR 将第二条相加指令保存, 并送入译码电路 EC, EC 译码并输出 IA=1, RR 寄存器 Q4=1, 译码器输入 IA=1, 输出 Iar=1;

第十四次按动开关 K, 寄存器 AR 存储存储新的地址值, RR 寄存器 Q5=1, 译码器输出 Idr=1, Ird=1, 存储器读出相加指令的操作数 5;

第十五次按动开关 K, 寄存器 DR 存储操作数 5, RR 寄存器 Q6=1, 译码器输出 Iac=1;

第十六次按动开关 K, 地址计数器 AC 再加一, RR 寄存器 Q7=1, 译码器输出 Itr=1, Iga=1, 传输门 GA 打开, 数据到达加法器 B 输入端, 加法器将之前装载的数 10 和现在的数 5 相加, 结果是 15;

第十七次按动开关 K, RR 寄存器 Q8=1, 寄存器 TR 把和值 15 存储, 译码器输出 Ira=1, Igb=1, 传输门 GB 打开, 和被反馈到寄存器 RA 的输入端;

第十八次按动开关 K, RR 寄存器 Q0=1, 又完成一次循环, 反馈的和被寄存器 RA 存储, 译码器输出 Iar=1, 传输门 GB 关闭.

重复按动开关 K, 直至取出所有指令及操作数, 完成累加.

原图