第11章 全自动加法计算机--带地址译码器的内存模型

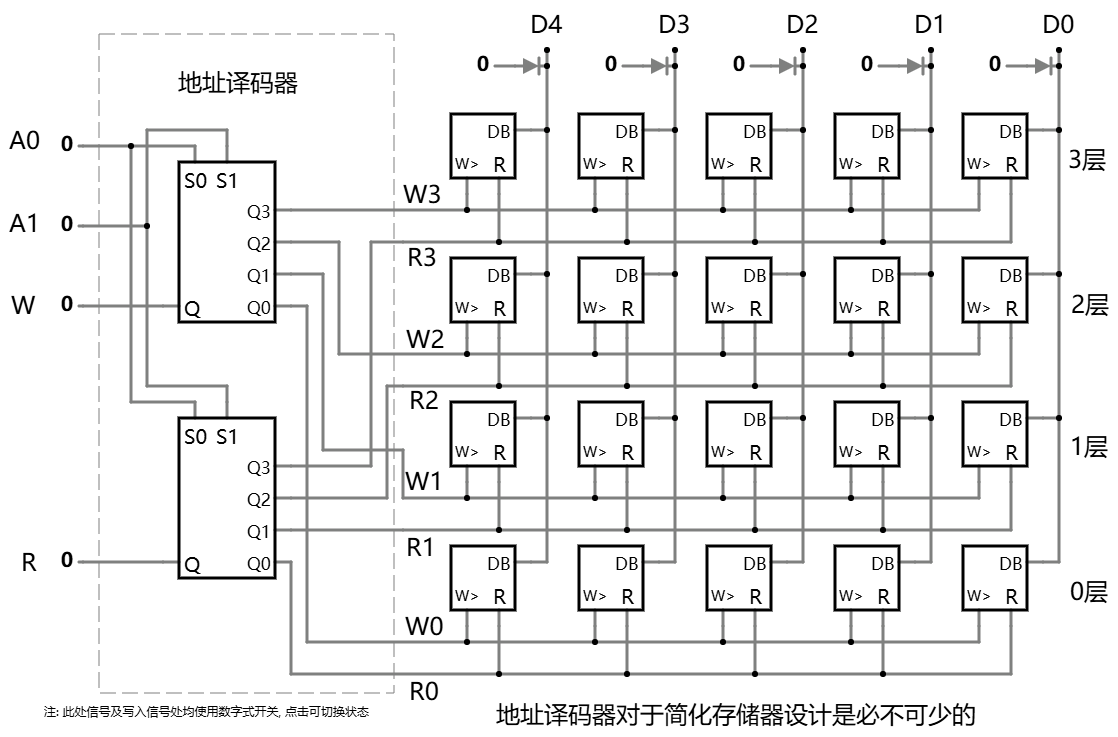

地址译码器

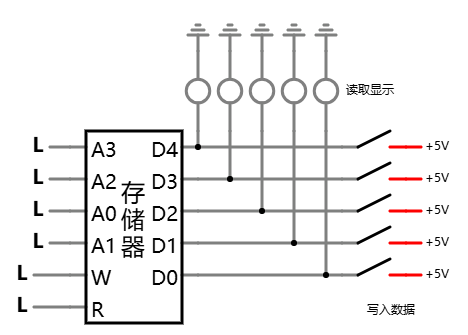

操作说明

书中没有给出具体的实现电路. 这里根据电路特性采用自定义逻辑实现.

关于 "自定义逻辑", 可参考此链接的说明: https://book.xiaogd.net/usage-of-circuitjs/circuitjs-custom-logic.html

这里本质上就是利用两个 2-4 译码器分别控制读和写.

注: 在系统中, 译码器被称为信号分离器(demultiplexer), 可通过 "菜单--绘制--数字芯片--添加信号分离器" 添加

鼠标单击逻辑输入切换 0|1 状态

先用 A0-A1 两根地址线选中 Q0~Q3 其中一组进行

W 和 R 开关控制写和读.

默认存储的都是 0 值, 读者可先尝试写入一些不一样的值, 才尝试读出来.

注: 因避免同时进行读写操作

另: 写操作时, 上方 D0~D4 处也引入了写入开关, 二极管是防止产生倒流

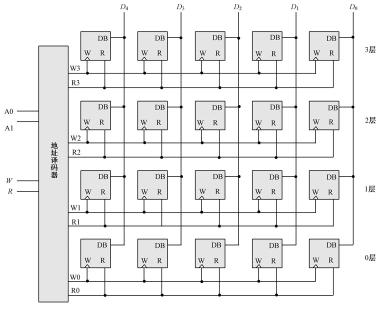

原图

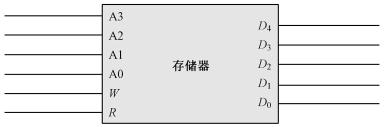

封装后的存储器整体外观

操作说明

上述电路封装后的结果

注: 此处是四根地址线, 可存储 16 组 5 比特单元

原图